Сравнение двоичных чисел | Основы электроакустики

Главная » Микросхемы

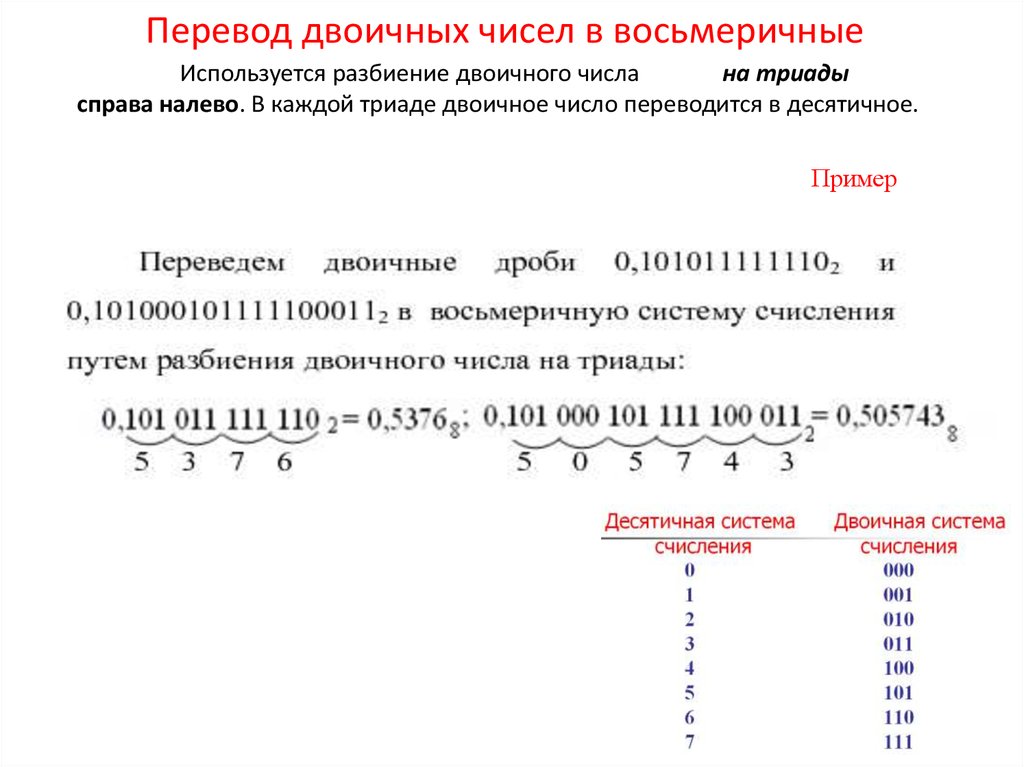

Сравнение двоичных чисел Сравнение многоразрядных чисел основывается на проверке равенства цифр чисел. Пусть даны два числа А3А2А1А0 и В3В2В1В0 . Сравниваются В3 и А3 , В2 и А2 , В1 и А1 , В0 и А0 , по результатам сравнения делается вывод: если совпали и третьи цифры, и вторые, и первые, и нулевые, то числа одинаковы. Таблица истинности поразрядного сравнения изображена на рис. 22.7.

рис. 22.7. Таблица истинности поразрядного сравнения

С помощью законов алгебры логики возможно представить выражение выходного сигнала:

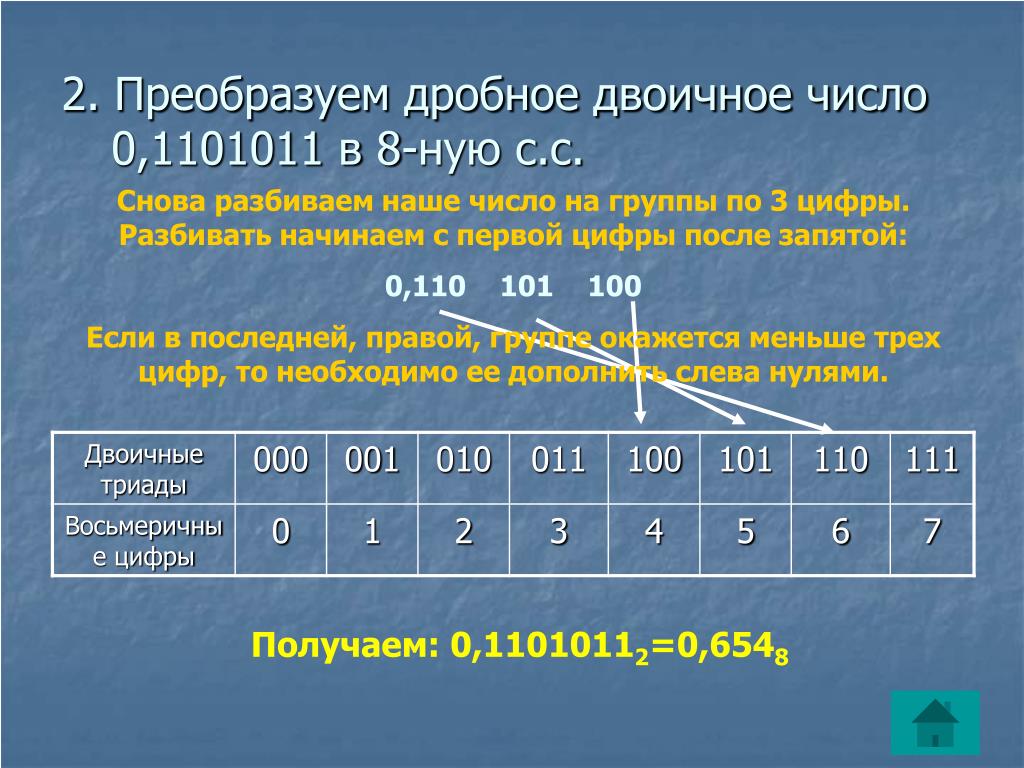

Переключательную функцию F позволяют реализовать логические двухвходовые элементы «Исключающее ИЛИ». На рис. 22.8 показан один из вариантов реализации схемы сравнения.

Рис. 22.8. Реализация схемы сравнения на ИС 155ЛП5 и 155ЛР3

Возможно построение более сложной схемы сравнения, которая определяет равенство чисел, а также, какое из чисел больше. Она может определять равенство двух двоичных чисел А и В с одинаковым количеством разрядов либо вид неравенства А > В или А < В. Цифровые компараторы имеют три выхода. Схема одноразрядного компаратора представляет собой структуру логического элемента «Исключающее ИЛИ-НЕ» (рис. 22.9).

Она может определять равенство двух двоичных чисел А и В с одинаковым количеством разрядов либо вид неравенства А > В или А < В. Цифровые компараторы имеют три выхода. Схема одноразрядного компаратора представляет собой структуру логического элемента «Исключающее ИЛИ-НЕ» (рис. 22.9).

Рис. 11.9. Цифровой компаратор с тремя выходами

Из анализа схемы следует, что если А = В, то F = 1, в противном случае, т.е. при А ≠ В, F = 0. Если А > В, т. е. А = 1, В = 0, то С = 1, а если А < В, т.е. А = 0, В = 1, то D = 1.

Если попарно равны между собой все разряды двух n-разрядных двоичных чисел, то равны и эти два числа А и В. Применяя цифровой компаратор для каждого разряда, например, четырехзначных чисел, и определяя значения F1, F2, F3, F4 логических переменных на выходах компараторов, факт равенства А = В установим в случае, когда F = F1• F2 • F3 • F4 = 1. Если же F = 0, то А ≠ В.

Неравенство А > В обеспечивается (для четырехразрядного числа) в четырех случаях: или А4 > В4, или А4 = В4 и А3 > В3, или А4 = В4, А3 = В3 и А2 > В2, или А4 = В4, А3 = В3, А2 = В2 и A1 > B1 (где А4 и В4 – старшие разряды чисел А и В). Очевидно, что если поменять местами Ai и Вi, то будет выполняться неравенство А < В.

Очевидно, что если поменять местами Ai и Вi, то будет выполняться неравенство А < В.

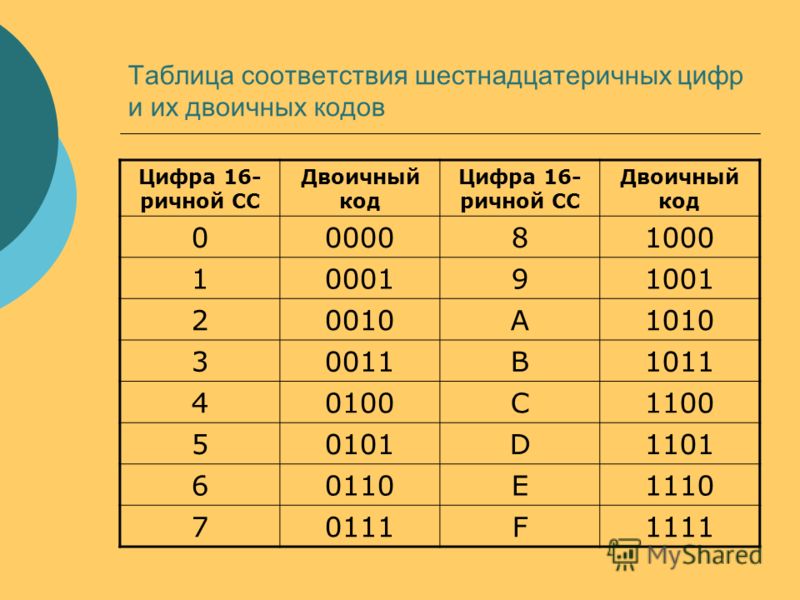

В настоящее время промышленностью выпускаются готовые четырехразрядные схемы сравнения чисел (рис. 22.10).

Рис. 22.10. Цифровые компараторы: а) К134СП1, б) К555СП1

Представленные микросхемы являются четырехразрядными компараторами, в которых каждый из одноразрядных компараторов аналогичен рассмотренной ранее схеме. Данные микросхемы имеют расширяющие входы А < В, А = В, А >В, что позволяет наращивать разрядность обоих чисел.

Сумматоры Суммирование двоичных чисел

Вычитание двоичных чисел

Переход от десятичных чисел к двоичным

Дешифраторы и шифраторы

Аналоговые компараторы напряжения Устройство и принцип действия

Простейшие компараторы на операционных усилителях

Логические элементы

Компараторы на интегральных микросхемах

Цифровые устройства

Цифровые устройства

ОглавлениеПредисловиеГлава 1. Основы теории переключательных функций 1.  2. Позиционные системы счисления 2. Позиционные системы счисления1.3. Переключательные функции 1.4. Принцип и закон двойственности 1.5. Теоремы разложения 1.6. Решение систем логических уравнений 1.7. Первичные термы, минтермы и макстермы 1.8. Совершенные нормальные формы представления функций 1.9. Конъюнктивные и дизъюнктивные термы 1.10. Минимизация переключательных функций 1.11. Диаграммы Вейча 1.12. Минимизация неполностью определенных функций, совместная минимизация нескольких функций 1.13. Скобочные формы функций 1.14. Закон двойственности для логических схем 1.15. Линейные функции Глава 2. Анализ и синтез логических схем 2.2. Модели логических элементов 2.3. Модели логических схем 2.4. Анализ логических схем 2.5. Синтез комбинационных схем, свободных от состязаний Глава 3. Синтез асинхронных потенциальных автоматов 3.2. Асинхронные потенциальные автоматы 3.3. Асинхронные потенциальные триггеры и элементы памяти Триггеры типа R-S Триггеры типа D-L Триггеры типа D-L-R с приоритетом входа R.  Триггеры типа D-L-R с приоритетом входа L. Триггеры типа R-S-L. Триггеры типа DN-LN Аналитический метод синтеза и анализа триггеров. 3.4. Задание асинхронных потенциальных автоматов таблицами и графами переходов 3.5. Синтез асинхронных потенциальных счетчиков 3.6. Синтез асинхронных импульсных триггеров Классификация триггеров. 3.7. Синтез синхронных триггеров Триггеры типа J-K Синхронно-асинхронные триггеры. 3.8. Примеры синтеза асинхронных потенциальных автоматов Цифровые фазочастотные детекторы. Квантизатор временных интервалов. 3.9. Генераторы сигналов Автогенераторы. Управляемые автогенераторы. Глава 4. Синтез синхронных автоматов 4.2. Синхронные триггеры Триггеры типов D и R-S с импульсным тактовым сигналом. Синхронные триггеры типов R-S и D-L Синхронно-асинхронные триггеры. Синхронные триггеры типа J-K Триггеры типа Т. Классификация синхронных триггеров. Преобразования типов синхронных триггеров.  Триггеры типов D-T-L и D-T-L/R Функции переходов синхронно-асинхронных триггеров. 4.3. Примеры синтеза синхронных автоматов 4.4. Сдвигающие регистры Синтез счетчиков на сдвигающих регистрах. Сдвигающие регистры с загрузкой данных. Реверсивные сдвигающие регистры. 4.5. Синхронные счетчики Синхронные двоичные счетчики. Синхронные двоично-десятичные счетчики. Каскадирование двоичных и двоично-десятичных счетчиков. Синхронные двоичные реверсивные счетчики. Реверсивные двоично-десятичные счетчики. Каскадирование реверсивных счетчиков. Счетчики на сдвигающих регистрах. Кольцевые счетчики. Линейные счетчики. Программируемые счетчики. 4.6. Асинхронные счетчики Асинхронные счетчики с умножением частоты счетного сигнала. Асинхронные импульсно-потенциальные счетчики. Асинхронное программирование модуля пересчета счетчиков. Глава 5. Логические элементы и триггеры Логические элементы. Классификация ИС по степени интеграции.  5.2. Интегральные схемы КМОП серий 5.4. Логические элементы с открытым коллекторным выходом Логические элементы с открытым коллекторным выходом. Применения ЛЭ с открытым коллекторным выходом. Интерфейсные ЛЭ с открытым коллекторным выходом. Логические элементы с открытым стоковым выходом. Типовые цоколевки ИС. 5.5. Логические элементы с тремя состояниями выхода Шинные драйверы с Z-состоянием выхода. Основные правила графического изображения ИС. 5.6. Преобразователи уровней напряжения и тока 5.7. Асинхронные потенциальные триггеры и регистры памяти 5.8. Синхронные триггеры и регистры памяти 5.9. Шинные приемопередатчики Шинные приемопередатчики с Z-состоянием выхода. Шинные приемопередатчики с открытым коллекторным выходом. Шинные приемопередатчики с регистрами памяти. Шинные приемопередатчики со сдвигающим регистром. Шинные трехнаправленные приемопередатчики. 5.10. Мультивибраторы 5.  11. Генераторы 11. ГенераторыСхемы устранения “дребезга” механических контактов. Автогенераторы периодических сигналов. 5.12. Рекомендации по выбору серий ИС Глава 6. Коммутаторы и арифметические устройства 6.1. Дешифраторы 6.2. Демультиплексоры 6.3. Мультиплексоры Мультиплексоры без стробирования. Мультиплексоры со стробированием. Мультиплексоры с Z-состоянием выхода. Каскадирование мультиплексоров. Функциональные мультиплексоры. Регистры памяти с мультиплексными входами данных. Мультиплексоры с регистрами памяти данных и адреса. Сдвигающие мультиплексоры. 6.4. Синтез комбинационных схем и цифровых автоматов на мультиплексорах Синтез схем на 8-канальных мультиплексорах. Синтез на двухразрядных 4-канальных мультиплексорах. Синтез генератора синусоидальной функции на мультиплексорах. Синтез триггеров на мультиплексорах. Синтез счетчиков на мультиплексорах. 6.  6. Шифраторы 6. Шифраторы6.7. Цифровые компараторы Программируемые цифровые компараторы. Адресные компараторы. Применения адресных компараторов. 6.8. Схемы сравнения двоичных чисел 8-разрядные схемы сравнения двоичных чисел. 6.9. Прямой, обратный и дополнительный коды Дополнительный код. Сложение чисел в обратном коде. Код с избытком 3. 6.10. Сумматоры Двоичные параллельные сумматоры с последовательным переносом. Двоичные сумматоры с параллельным переносом. Применения сумматоров. Десятичные сумматоры. Последовательные двоичные сумматоры. 6.11. Арифметическо-логические устройства 6.12. Пороговые схемы и мажоритарные элементы 6.13. Умножители двоичных чисел Быстрые умножители. БИС умножителя 12×12 разрядов 1802ВР4. Последовательные умножители. 6.14. Конвейерные устройства Конвейерный быстрый умножитель. Конвейерные АЦП. 6.15. Синтез линейных комбинационных схем Сумматор по модулю q. Умножитель по модулю q.  Глава 7. Сдвигающие регистры и счетчики 7.1. Сдвигающие регистры без параллельной записи данных Сдвигающие устройства с выходными регистрами памяти. 7.2. Сдвигающие регистры с параллельной записью данных Сдвигающие регистры с расширением знака. Сдвигающие регистры с входным регистром памяти. 7.3. Реверсивные сдвигающие регистры Реверсивные сдвигающие регистры типов PI/SO и PI/PO. Многофункциональные устройства на основе реверсивных сдвигающих регистров. 7.4. Асинхронные счетчики Двоично-десятичные асинхронные счетчики. 7.5. Синхронные двоичные счетчики Программирование модуля пересчета двоичных счетчиков. Функциональные устройства на основе двоичных счетчиков. 7.6. Синхронные двоично-десятичные счетчики 7.7. Синхронные реверсивные счетчики 7.8. Счетчики с расщепленным тактовым сигналом 7.9. Счетчики на сдвигающих регистрах 7.10. Кольцевые счетчики 7.11.  Делители частоты Делители частотыНормированные умножители частоты. 7.12. Линейные генераторы Приложение 1. Перечень отечественных и зарубежных ИС Приложение 2. Параметры интегральных схем |

Двоичный файл — SparkFun Learn

Авторы: Джимблом

Избранное Любимый 52

Существует несколько способов работы с двоичными значениями. Точно так же, как с десятичными числами, вы можете выполнять стандартные математические операции — сложение, вычитание, умножение, деление — с двоичными значениями (о которых мы поговорим на следующей странице). Вы также можете манипулировать отдельными битами двоичного значения, используя побитовые операторы .

Побитовые операторы выполняют функции побитно над одним или двумя полными двоичными числами. Они используют логическую логику, работающую с группой двоичных символов. Эти побитовые операторы широко используются как в электронике, так и в программировании.

Они используют логическую логику, работающую с группой двоичных символов. Эти побитовые операторы широко используются как в электронике, так и в программировании.

Дополнение (НЕ)

Дополнение двоичного значения похоже на нахождение полной противоположности всего, что в нем есть. Функция дополнения смотрит на число и превращает каждые 1 в 9.0015 0 и каждый 0 становится 1 . Оператор дополнения также называется

Например, чтобы найти дополнение 10110101:

НЕ 10110101 (десятичное число 181)

"="

01001010 (десятичное число 74)

NOT — единственный побитовый оператор, который работает только с одним двоичным значением.

ИЛИ

ИЛИ берет два числа и производит их объединение . Вот процесс ИЛИ двух двоичных чисел вместе: выровняйте каждое число так, чтобы биты совпадали, затем сравните каждый из их битов, которые имеют общую позицию. Для каждого битового сравнения, если один или оба бита равны 1, значение результата в этой битовой позиции равно 1. Если оба значения имеют 0 в этой позиции, результат также получает 0 в этой позиции.

Если оба значения имеют 0 в этой позиции, результат также получает 0 в этой позиции.

Четыре возможных комбинации ИЛИ и их результат:

- 0 ИЛИ 0 = 0

- 0 ИЛИ 1 = 1

- 1 ИЛИ 0 = 1

- 1 ИЛИ 1 = 1

Например, чтобы найти 10011010 ИЛИ 01000110, выровняйте каждое из чисел побитно. Если один или оба числа имеют 1 в столбце, значение результата также имеет 1 :

10011010 ИЛИ 01000110 "=" 11011110

Думайте об операции ИЛИ как о двоичном сложении без переноса. 0 плюс 0 равно 0, но 1 плюс что угодно будет 1.

И

И берет два числа и производит их соединение . AND выдаст 1 только в том случае, если оба значения, с которыми он работает, также равны 1 .

Процесс объединения двух двоичных значений по И аналогичен процессу ИЛИ. Выровняйте каждое число так, чтобы биты совпадали, затем сравните каждый из их битов, которые имеют общую позицию. Для каждого битового сравнения, если один или оба бита равны 0 , значение результата в этой битовой позиции равно 0 . Если оба значения имеют 1 в этой позиции, результат также получает 1 в этой позиции.

Для каждого битового сравнения, если один или оба бита равны 0 , значение результата в этой битовой позиции равно 0 . Если оба значения имеют 1 в этой позиции, результат также получает 1 в этой позиции.

Четыре возможных комбинации И и их результат:

- 0 И 0 = 0

- 0 И 1 = 0

- 1 И 0 = 0

- 1 И 1 = 1

Например, чтобы найти значение 10011010 И 01000110, начните с выстраивания каждого значения в ряд. Результат каждой битовой позиции будет только 1 , если оба бита в этом столбце также равны 1 .

10011010

И 01000110

"="

00000010

Думайте об И как о чем-то вроде умножения. Всякий раз, когда вы умножаете на 0, результат также будет 0.

XOR

XOR — это исключающее ИЛИ . XOR ведет себя как обычное ИЛИ, за исключением того, что только выдает 1 , если одно или другое число имеет 1 в этой битовой позиции.

Четыре возможных комбинации XOR и их результат:

- 0 XOR 0 = 0

- 0 Исключающее ИЛИ 1 = 1

- 1 Исключающее ИЛИ 0 = 1

- 1 Исключающее ИЛИ 1 = 0

Например, чтобы найти результат 10011010 XOR 01000110:

10011010

XOR 01000110

"="

11011100

Обратите внимание на бит 2 nd , 0 , полученный в результате двух операций XOR 1 вместе.

Битовые сдвиги

Битовые сдвиги не обязательно являются побитовыми операциями, подобными перечисленным выше, но они представляют собой удобный инструмент для работы с одним двоичным значением.

Битовый сдвиг состоит из двух компонентов: направление и количество бит для сдвига. Вы можете сдвинуть число либо на влево, либо на вправо, а также на один или несколько битов.

При сдвиге вправо один или несколько младших битов (в правой части числа) просто обрезаются, сдвигаются в бесконечное ничто. Ведущие нули могут быть добавлены, чтобы сохранить одинаковую длину бита.

Ведущие нули могут быть добавлены, чтобы сохранить одинаковую длину бита.

Например, сдвиг 10011010 на два бита вправо:

ПРАВЫЙ SHIFT-2 10011010 (десятичное число 154)

"="

00100110 (десятичное число 38)

Сдвиг влево складывает все биты в направлении старшей (левой) стороны числа. При каждом сдвиге в позицию младшего бита добавляется ноль.

Например, сдвиг 10011010 на один бит влево:

LEFT-SHIFT-1 10011010 (десятичное число 154)

"="

100110100 (десятичное число 308)

Этот простой битовый сдвиг на самом деле выполняет относительно сложную математическую функцию. Сдвиг влево n бит умножает число на 2 n (посмотрите, как в последнем примере ввод умножается на два?), а сдвиг n бит вправо приведет к делению целого числа на 2 п . Сдвиг вправо для деления может стать странным — любые дроби, полученные при делении сдвига, будут отсечены, поэтому 154, сдвинутое дважды вправо, равняется 38, а не 154/4=38,5. Битовые сдвиги могут быть очень быстрым способом деления или умножения на 2, 4, 8 и т. д.

Битовые сдвиги могут быть очень быстрым способом деления или умножения на 2, 4, 8 и т. д.

Эти побитовые операторы предоставляют нам большинство инструментов, необходимых для выполнения стандартных математических операций над двоичными числами.

справочный вопрос — Как компьютер определяет, является ли число меньше или больше другого?

спросил

Изменено 5 лет, 11 месяцев назад

Просмотрено 31к раз

$\begingroup$

Это может показаться глупым вопросом, но мне действительно любопытно узнать, как компьютер узнает, что $1<2$? Кроме того, откуда компьютер знает, что порядок целых чисел равен $1,2,3,4,5,\ldots$, а алфавит — A,B,C,D,...? Хранится ли она где-то в оборудовании или операционная система предоставляет такую информацию?

- компьютерная архитектура

- справочный вопрос

$\endgroup$

3

$\begingroup$

Сначала ваши целые числа преобразуются в двоичные числа. Например, целое число 2 преобразуется в 0010.

Например, целое число 2 преобразуется в 0010.

ЦП использует цифровой компаратор:

Цифровой компаратор или компаратор величин представляет собой аппаратное электронное устройство, которое принимает на вход два числа в двоичной форме и определяет одно число больше или меньше или равно другому число.

Компараторыиспользуются в центральных процессорах (ЦП) и микроконтроллерах.

Источник: https://en.wikipedia.org/wiki/Digital_comparator

В компараторах используются некоторые вентили (И, ИЛИ, И-НЕ, ИЛИ-НЕ, XOR и т.д.). Эти вентили принимают двоичные входы и дают результат в двоичном виде. Результат можно увидеть из таблицы истинности.

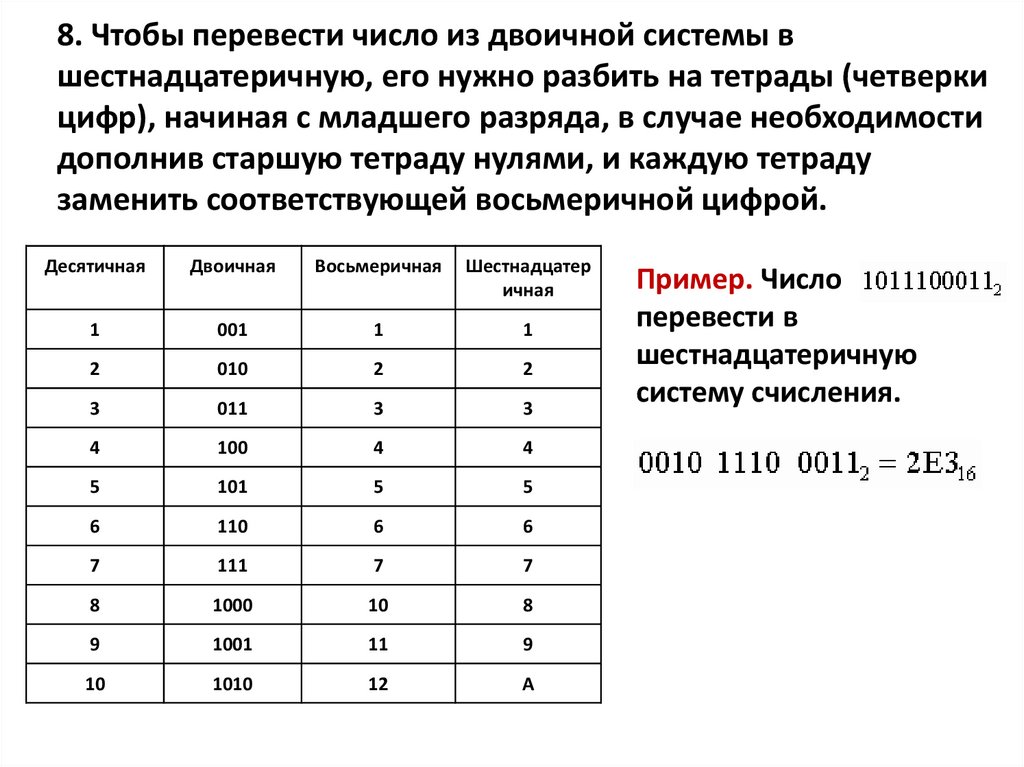

Входы Выходы А В А>В А=В А<В 0 0 0 1 0 0 1 0 0 1 1 0 1 0 0 1 1 0 1 0

Здесь 0 и 1 — электронные напряжения для затвора.

1 - Представляет некоторое пороговое напряжение, которое указывает на некоторое положительное напряжение.

0 - Представляет напряжение ниже порогового значения.

предположим, что компаратор работает на 5 вольт (это рассмотрение для объяснения), тогда:

Напряжение более 3 вольт можно рассматривать как двоичный-1 .

Напряжение ниже 3 вольт считается двоичным-0

Если вентиль получает один вход как 3,5 вольта, а другой вход как 2 вольта, то он считает, что он принимает один вход как двоичную 1, а другой вход как двоичный 0.

Эти последовательности 1 и 0 обеспечиваются очень быстро через схема переключения.

Работа двухбитного цифрового компаратора может быть выражена в виде таблицы истинности:

Входы Выходы

А1 А0 В1 В0 А>В А=В А<В

0 0 0 0 0 1 0

0 0 0 1 1 0 0

0 0 1 0 1 0 0

0 0 1 1 1 0 0

0 1 0 0 0 0 1

0 1 0 1 0 1 0

0 1 1 0 1 0 0

0 1 1 1 1 0 0

1 0 0 0 0 0 1

1 0 0 1 0 0 1

1 0 1 0 0 1 0

1 0 1 1 1 0 0

1 1 0 0 0 0 1

1 1 0 1 0 0 1

1 1 1 0 0 0 1

1 1 1 1 0 1 0

Цитата из Википедии:

Примеры: Рассмотрим два 4-битных двоичных числа A и B, такие что

Здесь каждый нижний индекс представляет одну из цифр в числах.Равенство

Двоичные числа A и B будут равны, если все пары значащих цифр обоих чисел равны, то есть

. . .Поскольку числа двоичные, цифры равны 0 или 1, а логическая функция равенства любых двух цифр и > может быть выражена как

равно 1, только если и равны.

Для равенства A и B все переменные (при i=0,1,2,3) должны быть равны 1. Таким образом, условие качества A и B может быть реализовано с помощью операции И как

Двоичная переменная (A=B) равна 1, только если все пары цифр двух чисел равны.Неравенство

Чтобы вручную определить большее из двух двоичных чисел, мы проверяем относительные величины пар значащих цифр, начиная с самого старшего бита, постепенно переходя к младшим значащим битам, пока не будет найдено неравенство. Когда неравенство найдено, если соответствующий бит A равен 1, а бит B равен 0, мы заключаем, что A>B. Это последовательное сравнение можно логически выразить так:

$\endgroup$

4

$\begingroup$

Он не просто "знает", он каждый раз проверяет. По сути, он делает то же самое, что и вы: для сравнения он проверяет (слева направо), у какого числа первая цифра больше, чем соответствующая цифра в другом числе. Конечно, вы должны добавить ведущие нули к более короткому числу.

По сути, он делает то же самое, что и вы: для сравнения он проверяет (слева направо), у какого числа первая цифра больше, чем соответствующая цифра в другом числе. Конечно, вы должны добавить ведущие нули к более короткому числу.

Буквы для компьютера - это просто цифры. Люди присвоили номера, например. ASCII или Unicode для букв, чтобы сравнение чисел также давало «правильный» порядок букв.

$\endgroup$

3

$\begingroup$

Не операционная система сравнивает целые числа, об этом заботится процессор. Это сделано на уровне логических элементов, пожалуйста, обратитесь к этим слайдам, чтобы увидеть, как это можно сделать.

Что касается алфавита, в ASCII буквенно-цифровые и другие специальные символы представлены как целые числа, поэтому их сравнение также является операцией сравнения целых чисел, которая выполняется ЦП.

$\endgroup$

0

$\begingroup$

На самом деле, и для того, чтобы получить полное представление о нем, я думаю, было бы весьма полезно увидеть своими глазами путь данных реального процессора, например MIPS:

Как видите, на самом деле есть второй выходной сигнал от АЛУ, который является сигналом, который называется Нуль. Он существует для выполнения быстрых операций ветвления после определения того, равны ли два операнда сравнения нулю или нет , поскольку большинство сравнений в программе связаны с ветвлениями. Поэтому, когда вы создаете в своем коде возможность перехода, например:

if(a < b) {...}

Это переводится в машинный код, например, в mips: blt s0,s1,If $~\Rightarrow$, если a < b выполнить инструкции в скобках, иначе продолжить выполнение за пределами if{}. В частности, эта инструкция является псевдоинструкцией, что означает, что она транслируется в две другие (простые) инструкции MIPS $~\Rightarrow$

В частности, эта инструкция является псевдоинструкцией, что означает, что она транслируется в две другие (простые) инструкции MIPS $~\Rightarrow$

slt at,s0,s1 и затем bne at,zero,If (slt: Set Меньше чем & bne: переход на не равно).

Обратите внимание, что нулевой сигнал является одним из входов логического элемента И, который определяет, откуда счетчик программ (ПК) будет получать свое значение: Предполагая, что сигнал перехода равен «1», так как у нас есть операция перехода

- Zero = 0 $\Rightarrow$ Результат вычитания не был равен нулю, поэтому Мультиплексор выберет адрес из Branch target и выполнение продолжится с инструкции, которую ведет ветвь.

- Ноль = 1 $\Rightarrow$ Результат был 0 (a = b) и поэтому MUX выбирает адрес из сумматора, где вычисляется адрес следующей инструкции в обычном исполнении (последовательном). Переход не выполняется, так как условие (a < b) недействительно.

Надеюсь, я помог вам заглянуть "под капот". Не стесняйтесь обращаться за дальнейшим анализом по этому вопросу. Многие вещи мы считаем само собой разумеющимися, процессоры делают их очень увлекательным образом!

$\endgroup$

1

$\begingroup$

Если вы хотите узнать, как это делает реальный ЦП, то вот что-то вроде этого.

ЦП работает только с числами определенного размера. В настоящее время это обычно 64-битные целые числа (мы будем игнорировать числа с плавающей запятой; идея будет аналогичной).

Таким образом, мы должны признать, что

ЦП хранит числа длиной до (скажем) 64 бита в двоичном формате в каком-то формате (вероятно, с дополнением до 2, но это не имеет большого значения).

ЦП изначально не может ничего делать с большими числами. Мы должны написать программные алгоритмы, если хотим сравнивать большие числа.

Итак, допустим, у нас есть два числа, каждое из которых соответствует 64-битному целому нормальному размеру. Произнесите $a$ и $b$. Как процессор их сравнивает? Обычно он вычитает одно из другого (это единственная встроенная операция, реализованная аппаратно).

Теперь процессор сохранил единственное число $a-b$. Опять же, это число имеет длину не более 64 бит, поэтому оно помещается в «регистр» длиной 64 бита, где мы храним наши числа для вычислений. Теперь он просто проверяет, меньше ли $a-b$ нуля. Он делает это с помощью одной собственной операции, которая может работать на уровне схемы, например алгоритмы сравнения, описанные в других ответах. Это будет очень похоже на эти, но все они реализованы в схемах (поскольку число имеет максимальную длину 64 бита, это схема определенного размера, которую мы можем жестко подключить и прикрепить к ЦП). В зависимости от того, как ЦП хранит числа, он может быть даже быстрее, потому что может случиться так, что все отрицательные числа имеют первый бит, равный единице, или что-то в этом роде. В любом случае, всего 64 бита, так что мы точно можем проверить, является ли это число отрицательным.

В любом случае, всего 64 бита, так что мы точно можем проверить, является ли это число отрицательным.

Если да, то мы знаем, что $a < b$; если нет, то мы знаем $a \geq b$.

Теперь, для больших чисел, мы должны реализовать что-то в программном обеспечении, которое будет использовать эти маленькие сравнения как подпрограммы.

$\endgroup$

$\begingroup$

Чтобы ответить на этот вопрос, позвольте мне сначала указать, что существует по крайней мере два уровня абстракции для чисел сравнения на компьютере: машинный уровень и программный уровень 9.0008 .

Сравнение чисел на машинном уровне

ЦП современного компьютера имеет богатый набор инструкций. Эти инструкции включают, например, загрузку ячейки памяти в регистр, увеличение регистра, добавление двух регистров и многое другое. Также должны быть инструкции для условных переходов . Например, процессоры семейства Intel x86 поддерживают инструкции

Например, процессоры семейства Intel x86 поддерживают инструкции jnz (переход, если не ноль), jne (переход не равен) и так далее. Если бы они отсутствовали, ЦП не был бы полным по Тьюрингу. Переменные, от которых зависит условный переход, хранятся в регистрах. Таким образом, эти инструкции жестко зашиты в архитектуре ЦП в виде схемы, построенной из логических вентилей. Это единственный способ, которым ЦП может сравнить два числа.

Сравнение чисел на программном уровне

Если вы сравниваете два числа, скажем, в программе на C++, то это преобразуется в машинный код и, следовательно, выполняется на машинном уровне. Однако такое сравнение может оказаться более сложным. Это действительно зависит от типа данных, который вы использовали, как сравнение преобразуется в машинный код. Только один пример: числа, которые вы хотите сравнить, взяты из 64-битных слов, но ваша машина работает только с 32-битными. Тогда это число не помещается в регистр, поэтому компилятор разбивает сравнение на последовательность сравнений на уровне машинного кода. То же самое относится и к более сложным типам данных/структурам данных, представляющим, например, рациональные числа, строки или символы. Следовательно, когда вам нужно сравнить два символа, это должно быть переведено программным обеспечением (операционной системой, компилятором, интерпретатором и т. д.) в машинный код. Фактический перевод зависит от кодировки символа/числа.

То же самое относится и к более сложным типам данных/структурам данных, представляющим, например, рациональные числа, строки или символы. Следовательно, когда вам нужно сравнить два символа, это должно быть переведено программным обеспечением (операционной системой, компилятором, интерпретатором и т. д.) в машинный код. Фактический перевод зависит от кодировки символа/числа.

В заключение хочу отметить, что стандартные процессоры также могут работать с различными представлениями чисел (целые числа со знаком в дополнении до 1 или 2, числа с плавающей запятой). Также сравнения могут быть проведены в других частях компьютера, таких как графический процессор.

$\endgroup$

$\begingroup$

другие ответы хороши, просто добавлю еще один для дальнейшего рассмотрения/понимания с привкусом/поворотом CS. можно построить FSM, конечный автомат, который может сравнивать два двоичных числа любой длины, начиная попарно со старших битов и работая до наименее значимого бита (LSB). его также можно использовать для концептуализации цифрового компаратора, данного в другом ответе, но FSM не требует двоичных чисел конечной длины. он может даже работать с целыми числами с двоичными дробями после LSB. он имеет индуктивный и рекурсивный характер, и его правильность может быть доказана с помощью простой индукции. работает следующим образом:

его также можно использовать для концептуализации цифрового компаратора, данного в другом ответе, но FSM не требует двоичных чисел конечной длины. он может даже работать с целыми числами с двоичными дробями после LSB. он имеет индуктивный и рекурсивный характер, и его правильность может быть доказана с помощью простой индукции. работает следующим образом:

- введите две старшие двоичные цифры как пару (a,b)

- , если a=1 и b=0, левое число больше.

- , если a=0 и b=1, правильное число больше.

- иначе числа "до сих пор равны", перейти к следующей паре.

, другими словами, наибольшее число — это число, в котором первое вхождение бита равно единице, а второе равно нулю после начального запуска из нуля или более идентичных единиц. цифровой компаратор конечной длины, состоящий из логических элементов или 1-битных компараторов, можно рассматривать как основанный на фиксировании длины этой операции FSM до некоторого фиксированного числа битов. (да, существует строгое соответствие между всеми конечными схемами и «фиксацией длины» вычислений FSM.)

(да, существует строгое соответствие между всеми конечными схемами и «фиксацией длины» вычислений FSM.)

это может показаться теоретическим упражнением, но на самом деле логика в программном обеспечении для представления чисел произвольной точности работает чем-то аналогичным этому автомату, за исключением того, что он закодирован в компьютерном цикле, который можно рассматривать как повторение или моделирование шагов конечного автомата. (эффективная реализация может отслеживать с помощью индекса местоположение MSB).

также позволяет разумно интерпретировать/обобщить этот вопрос как , не ограничиваясь целыми числами . вопрос относится к целым числам, но заголовок относится только к числам. удивительно, что до сих пор никто не упомянул арифметику с плавающей запятой. 9b$, $a$ мантисса, b показатель степени. мантисса может быть нормализована до числа, где первая цифра всегда отлична от нуля. затем, чтобы сравнить два числа, логика сначала сравнивает показатели степени $b$, и если они не равны, она может вернуть результат без сравнения мантиссы (используя, скажем, схему компаратора).

И., Новосельцева Т. Я. Цифровые устройства: Учебное пособие для втузов. — СПб.: Политехника, 1996. — 885 с.

И., Новосельцева Т. Я. Цифровые устройства: Учебное пособие для втузов. — СПб.: Политехника, 1996. — 885 с.